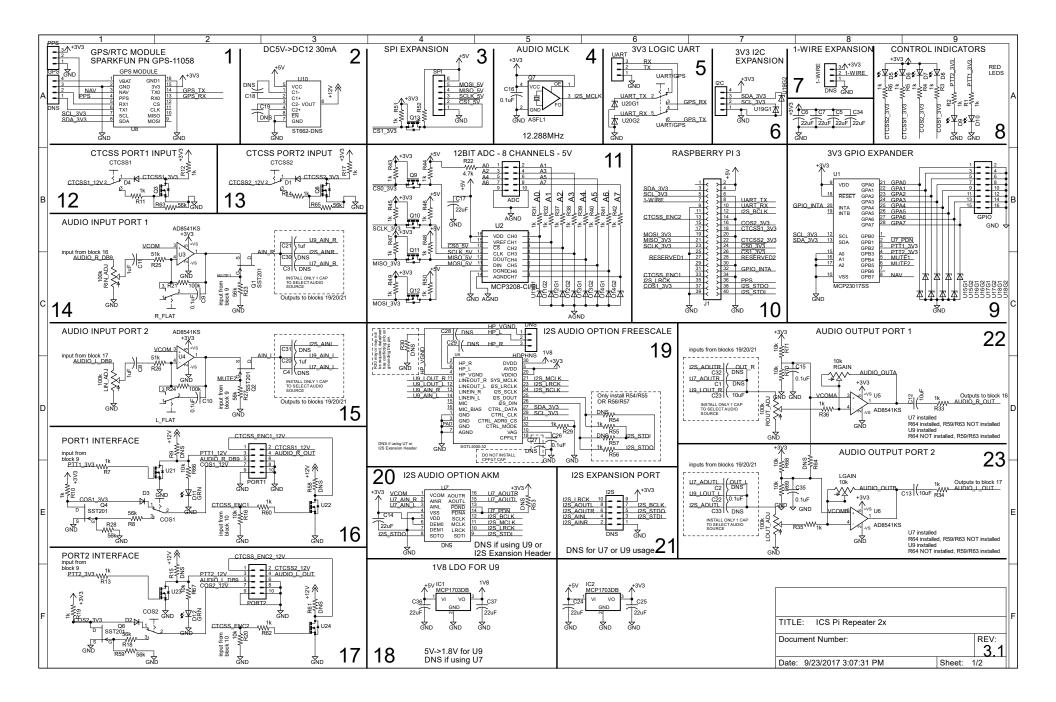

### **BASIC THEORY OF OPERATION BLOCK 1: GPS MODULE**

The Shelf GPS solution with an external antenna (sold seperately) designed and sold by SparkFun Electronics.

The unit will dock with this design to users who will be the line an effective and the set of the unit will dock with this design for users who will be the line an effective and the set of the unit will dock with the set of the set of the line and the set of the s

# BLOCK 3: 5V SPI BUS EXPANSION

neader is provided to allow for expansion of a single 5.0Vdc SPI protocol device. The signals are buffered by a FET logic

#### **BLOCK 4: AUDIO MCLK** s the PI platform cannot provide this clock to the chips natively. BLOCK 5: 3V3 LOGIC UART

This block provides a 3V3 logic level uart connection directly to the PI platform for debug use in case user does not have ethernet access, or wishes to use the GPS modules utilizes uart protocol for timing messages. These pins have a zener diode on the lines for limited protection against ESD and overvoltage.

For GPS usage, the switch must be moved to the GPS location which will disconnect the header from the PI device

#### BLOCK 6: 3V3 I2C EXPANSION This block provides a 3V3 logic level ulart connection directly to the PI platform for debug use in case user does not have etherned ta or where is use the GPS modules utilizes usit protocol for timing messages. These priors have a zeroer doed on the lines for limited et access

against ESD and overvoltage conditions

For GPS usage, the switch must be moved to the GPS location which will disconnect the header from the PI device

# BLOCK 7: 1-WIRE EXPANSION This port is provided to allow the user to utilize a 3V3 1-wire device, or expose the user clock source for external usages. This pit connected directly to the PI with NO PROTECTION. The user must handle all circuit protection needs related to this incruit.

### **BLOCK 8: LED INDICATORS**

The indicators are wired for active low signal conditions due to the input management circuits. When monitoring these signals, it is Interinductors are when to accere two signal continuous due to the input management circuits. When monitoring mese signals, it is important to remember the input management circuits will always output an active low signal to the processor regardless of the actual active state provided by the radio. This is discussed further in BLOCK 12/13.

# **BLOCK 9: GPIO EXPANDER**

A 16 BIT (2x8bit banks) is used to provide user accessible GPIO pins while still providing a laver of protection to the processor. Eight of the pins are exposed to the user and include a zener diode protection circuit for some limited protection of the device for ESD and overvoltage conditions. The GPIO are capable of driving or receiveing 3V3 TTL signals and may be configured on a pin by pin basis. Internal pull-ups are available on all pins if configured.

#### **BLOCK 10: PI3 INTERFACE** 2x20 Stacking Header for interconnecting with the PI3 header

# BLOCK 11: 8 CHANNEL 5V ADC

This block provides the user 8 channels of 12-bit ADC inputs with 5V capability. All channels are independently current limited and zener protected to help prevent damage. It is upon the user to configure each channel in the OpenRepeater GUI for their specific applications.

# **BLOCK 12/13: CTCSS INPUTS**

As the CTCSS input signals are 12V and may be either active HIGH or LOW, this circuit converts the signal to a 3V3 ACTIVE LOW

input to the PI. \*With an active HIGH input, the input should be fed to the FET gate, which will turn on the FET, pulling the PI input to ground. \*With an active LOW input, the input should be fed to the diode, which will forward bias the diode, pulling the PI input to ground.

# **BLOCK 14/15: AUDIO INPUTS**

This unit is designed to accept 1 channel each of mono input from the radios on port 1 and 2. A multi turn pot is used for input level adjust. This this designed to becche treatment of the other and the most of part and the second of part and the second of the part and the part becche to import and the part becche and the part of the part audio codec being used in the system

### **BLOCK 16/17: RADIO INTERFACES**

A 2x5 header and circuitry to interface with the radio \* PTT/CTCSS Encode is output as a 33% signal but act on a 12V signal to the radio the radio, so this signal is opto-isolated to the radio \*COS is received from the radio as a 12V signal so is protected and converted to an active LOW signal into the microcontroller. See Block 12/13 description for more detailed explanation of the circuitry behavior.

#### **BLOCK 18: 1V8 LDO REGULATOR** for providing the 1.8V required to power U9 CODEC. If U7 or the external I2S codec are used t

# **BLOCK 19-21: I2S AUDIO CODECS**

The design includes options for an AK4554VT as well as a SGTL5000, and also has provisions for a third external user designed audio codec interface. Only a single ISS device may installed on the hardware bus, if using the expander circuit, the ICS at U7 and U9 must be removed from the board and the appropriate capacitors relocated in blocks 14/15/22/23 to select the expansion header.

### **BLOCK 22/23: AUDIO OUTPUTS**

Similar to the input circuits, these blocks have a capacitor fork for selecting the source of the audio to receive into the output stages After the audio source selection capacitors is a level adjust potentiometer followed by an amplifier stage with a potentiometer for gain adjust. Following the amplifiers is a RC section for load impedace matching.

Due to the nature of the codecs, some output a common voltage while others do not. To handle this condition R59/R63/R64 are used to either bridge the common inputs (R64) or adjust individually the channels (R59/R63) for best amplifier centering.

| ITLE: | ICS Pi Repeater 2x |  |

|-------|--------------------|--|

т

| Document Number:      |       |        | ŀ  | REV: |

|-----------------------|-------|--------|----|------|

| Date: 9/23/2017 3:07: | 31 PM | Sheet: | 2/ | 2    |